- 您现在的位置:买卖IC网 > Sheet目录312 > AT24C256C-XHL-B (Atmel)IC EEPROM 256KBIT IND 8TSSOP

�� �

�

�

�7.�

�Device� Addressing�

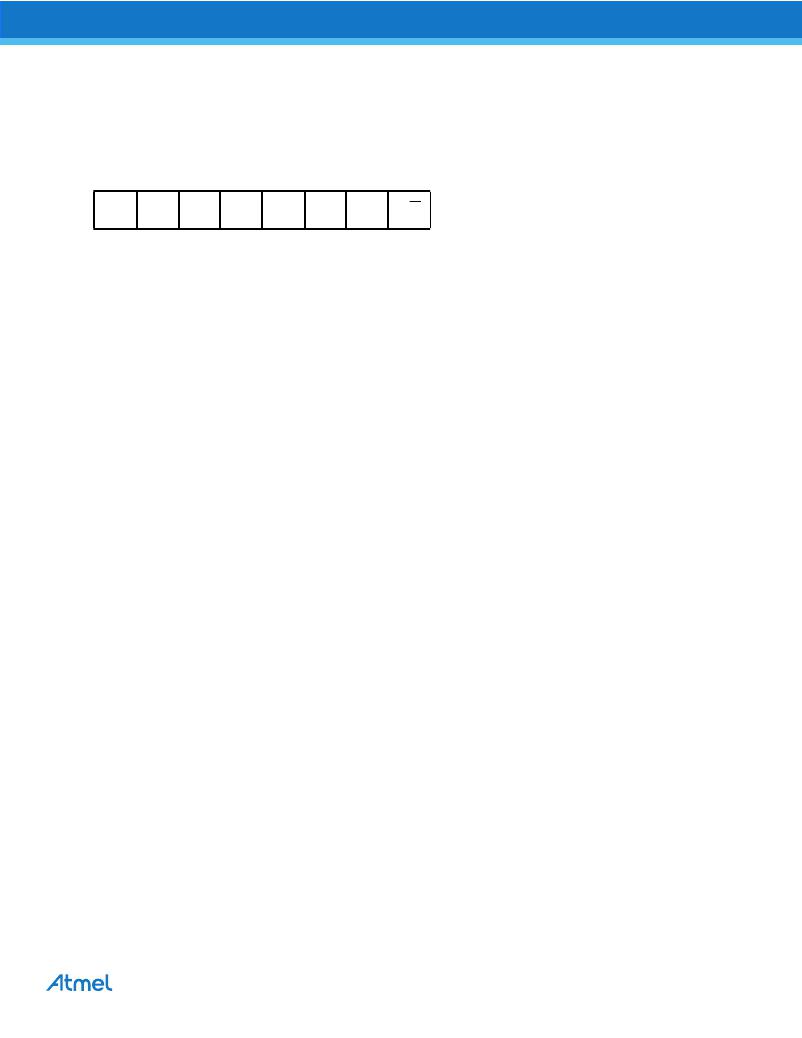

�The� 256K� EEPROM� requires� an� 8-bit� device� address� word� following� a� start� condition� to� enable� the� chip� for� a� read� or�

�write� operation� (� Figure� 7-1� ).� The� device� address� word� consists� of� a� mandatory� one,� zero� sequence� for� the� first� four� most�

�significant� bits� as� shown.� This� is� common� to� all� 2-wire� EEPROM� devices.�

�Figure� 7-1.� Device� Addressing�

�1�

�0�

�1�

�0�

�A2�

�A1�

�A0�

�R/W�

�MSB�

�LSB�

�The� next� three� bits� are� the� A2,� A1,� and� A0� device� address� bits� to� allow� as� many� as� eight� devices� on� the� same� bus.� These�

�bits� must� compare� to� their� corresponding� hard� wired� input� pins.� The� A� 2� ,� A� 1� ,� and� A� 0� pins� use� an� internal� proprietary� circuit�

�that� biases� them� to� a� logic� low� condition� if� the� pins� are� allowed� to� float.�

�The� eighth� bit� of� the� device� address� is� the� read/write� operation� select� bit.� A� read� operation� is� initiated� if� this� bit� is� high,�

�and� a� write� operation� is� initiated� if� this� bit� is� low.�

�Upon� a� compare� of� the� device� address,� the� EEPROM� will� output� a� zero.� If� a� compare� is� not� made,� the� device� will� return�

�to� a� standby� state.�

�Data� Security:� AT24C256C� has� a� hardware� data� protection� scheme� that� allows� the� user� to� write� protect� the� whole�

�memory� when� the� WP� pin� is� at� V� CC� .�

�Atmel� AT24C256C� [DATASHEET]�

�8568E–SEEPR–8/2012�

�9�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

AT24C32AY6-10YH-1.8

IC EEPROM 32KBIT 400KHZ 8DFN

AT24C512BY7-YH25-T

IC EEPROM 512KBIT 1MHZ 8SAP

AT24C512W-10SU-1.8

IC EEPROM 512KBIT 400KHZ 8SOIC

AT24C64B-10TU-1.8

IC EEPROM 64KBIT 400KHZ 8TSSOP

AT24C64CY6-YH-T

IC EEPROM 64KBIT 1MHZ 8MLP

AT24C64W-10SI-1.8

IC EEPROM 64KBIT 400KHZ 8SOIC

AT24HC02B-TH-B

IC EEPROM 2KBIT 1MHZ 8TSSOP

AT25040A-10TU-1.8

IC EEPROM 4KBIT 20MHZ 8TSSOP

相关代理商/技术参数

AT24C256C-XHL-T

功能描述:电可擦除可编程只读存储器 256K (32K X 8), 2-WI 1.8V RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8

AT24C256C-XPD-T

制造商:Atmel Corporation 功能描述:SERIAL EEPROM, 256K (32K X 8) - Tape and Reel

AT24C256N-10SC

功能描述:IC EEPROM 256KBIT 1MHZ 8SOIC 制造商:microchip technology 系列:- 包装:管件 零件状态:停產 存储器类型:非易失 存储器格式:EEPROM 技术:EEPROM 存储容量:256Kb (32K x 8) 时钟频率:1MHz 写周期时间 - 字,页:10ms 访问时间:550ns 存储器接口:I2C 电压 - 电源:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C(TA) 安装类型:表面贴装 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商器件封装:8-SOIC 基本零件编号:AT24C256 标准包装:100

AT24C256N-10SC-1.8

功能描述:IC EEPROM 256KBIT 400KHZ 8SOIC 制造商:microchip technology 系列:- 包装:管件 零件状态:停產 存储器类型:非易失 存储器格式:EEPROM 技术:EEPROM 存储容量:256Kb (32K x 8) 时钟频率:400kHz 写周期时间 - 字,页:10ms 访问时间:900ns 存储器接口:I2C 电压 - 电源:1.8 V ~ 3.6 V 工作温度:0°C ~ 70°C(TA) 安装类型:表面贴装 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商器件封装:8-SOIC 基本零件编号:AT24C256 标准包装:100

AT24C256N-10SC-2.7

功能描述:IC EEPROM 256KBIT 1MHZ 8SOIC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:32 系列:- 格式 - 存储器:闪存 存储器类型:FLASH 存储容量:1M (128K x 8) 速度:120ns 接口:并联 电源电压:2.7 V ~ 3.6 V 工作温度:0°C ~ 70°C 封装/外壳:32-LCC(J 形引线) 供应商设备封装:32-PLCC 包装:管件 其它名称:AT49BV00112JC

AT24C256N-10SI

功能描述:IC EEPROM 256KBIT 1MHZ 8SOIC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:32 系列:- 格式 - 存储器:闪存 存储器类型:FLASH 存储容量:1M (128K x 8) 速度:120ns 接口:并联 电源电压:2.7 V ~ 3.6 V 工作温度:0°C ~ 70°C 封装/外壳:32-LCC(J 形引线) 供应商设备封装:32-PLCC 包装:管件 其它名称:AT49BV00112JC

AT24C256N-10SI-1.8

功能描述:IC EEPROM 256KBIT 400KHZ 8SOIC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:32 系列:- 格式 - 存储器:闪存 存储器类型:FLASH 存储容量:1M (128K x 8) 速度:120ns 接口:并联 电源电压:2.7 V ~ 3.6 V 工作温度:0°C ~ 70°C 封装/外壳:32-LCC(J 形引线) 供应商设备封装:32-PLCC 包装:管件 其它名称:AT49BV00112JC

AT24C256N-10SI-2.7

功能描述:IC EEPROM 256KBIT 1MHZ 8SOIC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:32 系列:- 格式 - 存储器:闪存 存储器类型:FLASH 存储容量:1M (128K x 8) 速度:120ns 接口:并联 电源电压:2.7 V ~ 3.6 V 工作温度:0°C ~ 70°C 封装/外壳:32-LCC(J 形引线) 供应商设备封装:32-PLCC 包装:管件 其它名称:AT49BV00112JC